# **Chapter 2 : Semiconductor Materials & Devices (I)**

#### Reference

- 1. SemiconductorManufacturing Technology: Michael Quirk and Julian Serda (2001)

- 2. 國家矽導計畫-教育部晶片法商學程編定教材

- 3. ULSI Technology: C. Y. Chang, S. M. Sze (1996)

- 4. Semiconductor Physics and Devices- Basic Principles (3/e) : Donald A. Neamen (2003)

- 5. Semiconductor Devices Physics and Technology (2/e) : S. M. Sze (2002)

#### **Semiconductor Materials**

## - The Crystal Structure of Solids

- 何謂半導體?(基本半導體特性)

- 半導體之分類

- 半導體材料之結構

- 一般晶格所常用之術語

- 半導體材料之成長

#### 何謂半導體?

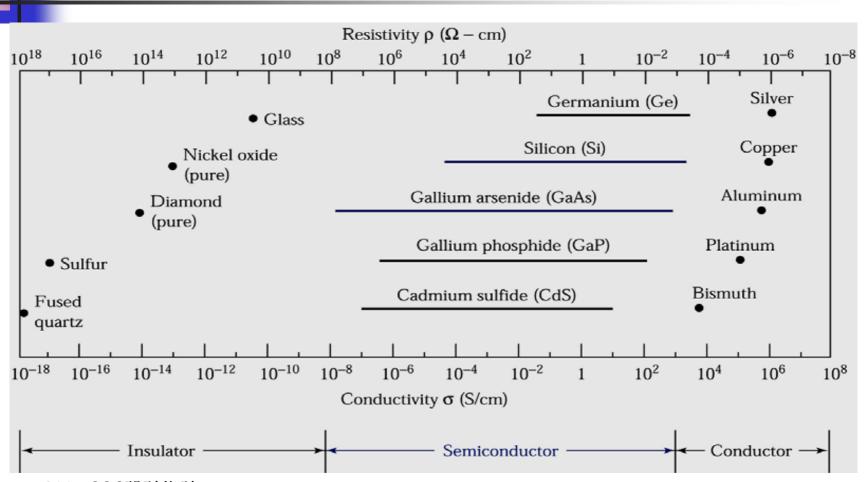

- •以通俗的字眼來說便是一種材料它的導電度介於金屬與非金屬之間:  $10^4 \sim 10^{-10} \, (\Omega \, \text{cm})^{-1}$ 。

- •以專業的眼光來看便是該材料的電阻值可藉由摻入雜質(impurity)的種類、數量來調整。

- •雜質種類的不同將可以決定載子(carrier)的型態。當有特定區域適合 這兩種型態的載子相互結合時,電子元件的種種特性便接踵而來。

#### What is Semiconductor

Conductivity between conductor and insulator

## 與半導體相關之週期元素 Element Semiconductors

| Period | Column II       | III        | IV          | V             | VI        |

|--------|-----------------|------------|-------------|---------------|-----------|

| 2      |                 | B<br>Boron | C<br>Carbon | N<br>Nitrogen |           |

| 3      | Mg              | Al         | Si          | P             | S         |

|        | Magnesium       | Aluminur   | Silicon     | Phosphorus    | Sulfur    |

| 4      | Zn              | Ga         | Ge          | As            | Se        |

|        | Zinc            | Gallium    | Germanium   | Arsenic       | Selenium  |

| 5      | Cd              | In         | Sn          | Sb            | Te        |

|        | Cadmium         | Indium     | Tin         | Antimon       | Tellurium |

| 6      | · Hg<br>Mercury |            | Pb<br>Lead  |               |           |

Why Silicon Can Dominate the IC Industry?

Silicon devices exhibit better properties at room temperature, and high-quality silicon dioxide can be grown thermally. There is also an economic consideration. Device-grade silicon costs much less than any other semiconductor material.

## 半導體分類

- 基本上以週期表的第四族為基準點,其共通特性是每一原子平均有四個價電子

- 事實上近年來材料的演進極為快速,凡是與電子元件工業相關連的材料都被統稱電子材料,而半導體材料的定義逐漸廣義化,凡是可以產生正負型載子的材料都可稱之半導體。

- 傳統上半導體材料依舊落於無機材料,近年來有機材料正被重視當中。

Table 2 Element and Compound Semiconductors

| Element | IV-IV<br>Compounds | III–V<br>Compounds | II–VI<br>Compounds | IV-VI<br>Compounds |

|---------|--------------------|--------------------|--------------------|--------------------|

| Si      | SiC                | AlAs               | CdS                | PbS                |

| Ge      |                    | AlSb               | CdSe               | PbTe               |

|         | ¥                  | BN                 | CdTe               |                    |

|         |                    | GaAs               | ZnS                |                    |

|         |                    | GaP                | ZnSe               |                    |

|         |                    | GaSb               | ZnTe               |                    |

|         |                    | InAs               |                    | 2.                 |

|         | 12.                | InP                | e ,                |                    |

|         |                    | InSb               |                    |                    |

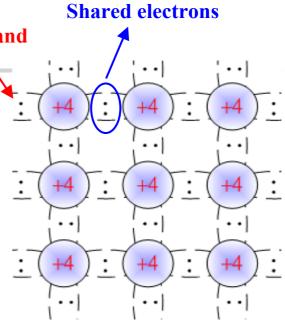

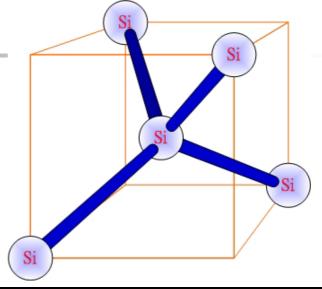

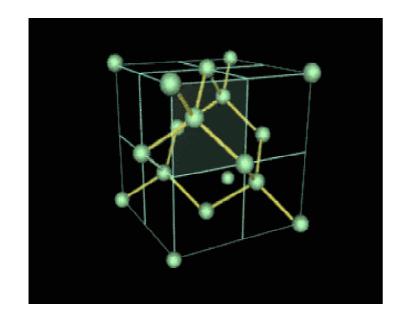

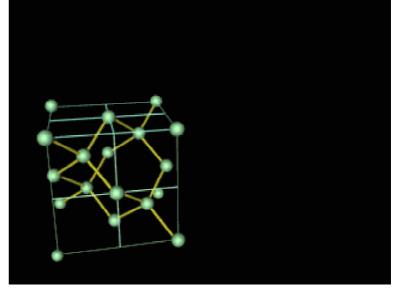

#### Silicon Structure

**Covalence band**

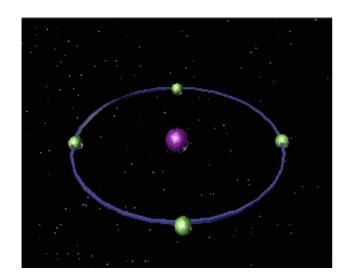

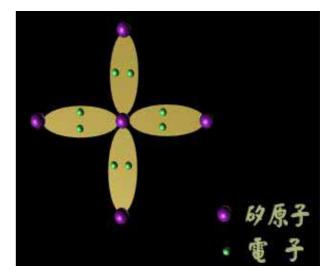

#### **Silicon Atom**

Quadrivalent element

Four valence electron

Atomic number = 14

4 valence electron

Covalent bond

#### **Silicon Structure**

#### **Diamond Structure**

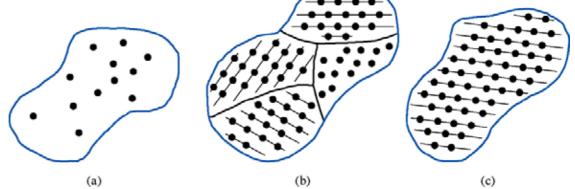

#### 半導體材料結構

一般材料結構可區分為非晶 系,多晶系以及單晶系。其 重大的區別在於原子排列規 則性持續的程度大小而定

Schematics of three general types of crystals:(a) amorphous, (b) polycrystalline, (c) single crystal.

**Amorphous materials** have order only within a few atomic or molecular dimensions.

<u>Polycrystalline materials</u> have a high degree of order over many atomic or molecular dimensions. These ordered regions, or single-crystal regions, vary in size and orientation with respect to one another. The single-crystal regions are called *grains* and are separated from one another by *grain boundaries*.

<u>Single-crystal materials</u>, ideally, have a high degree of order, or regular geometric periodicity, throughout the entire volume of the material. The advantage of a single-crystal material is that, in general, its electrical properties are superior to those of a non-single crystal material, since <u>grain boundaries tend to degrade the electrical characteristics</u>

.在半導體元件應用上,該三種型態結構都有其應用的價值。唯獨當元件是用來作為主動元件時,則該半導體 必須是單晶型態。

2005 SOC設計概論 中山電機系 黃義佑

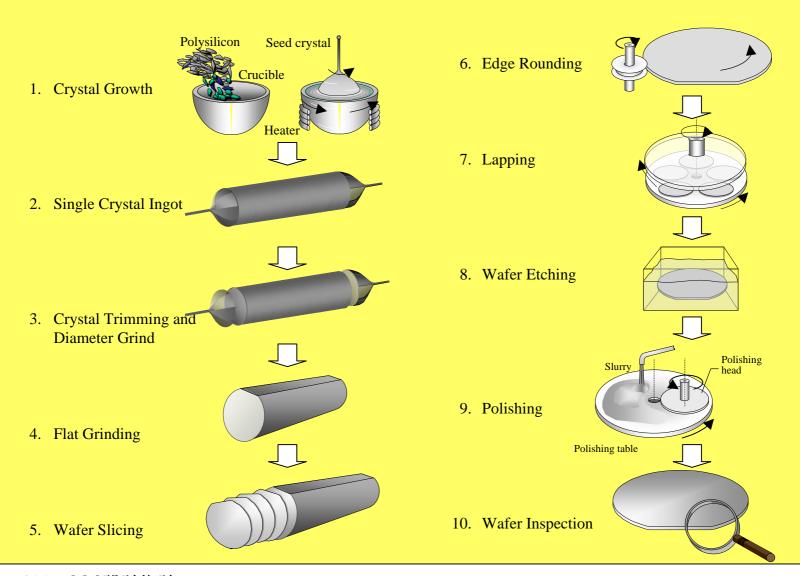

## **Preparation of Single Crystal Silicon Wafers**

Diameter: 10~30cm, 20cm(8-inch)

Thickness: 400~600µm

Resistivity:  $0.05 \sim 0.1 \Omega cm$

### 半導體材料成長

- ➢ 將純度不高之SiO₂在高溫下以碳還原成中純度之Si,然後利用HCI使其反應成SiHCI3的液體,再利用其沸點不同之特性加以蒸餾,最後形成高純度之Si塊

- 在融融狀態下以種晶在極慢的速度下拉晶

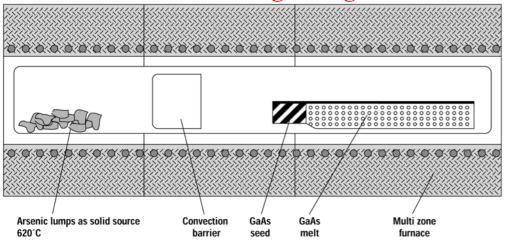

#### > 50% market for growing GaAs

2005 SOC設計概論 中山電機系 黃義佑

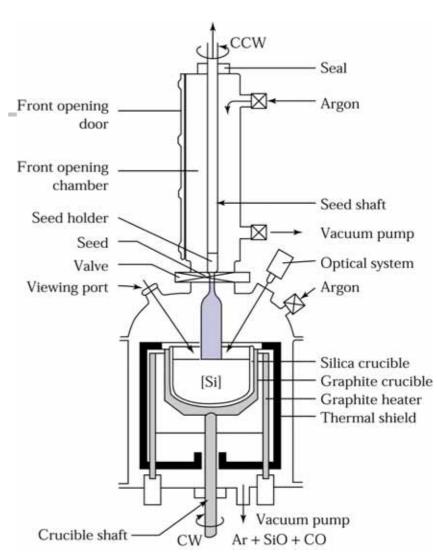

Simplified schematic drawing of the Czochralski puller. Clockwise (CW), counterclockwise (CCW).

#### Czochralski Growth

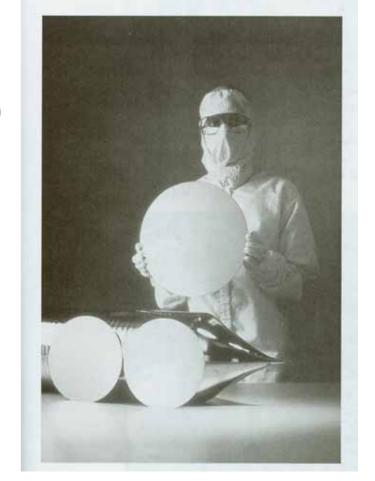

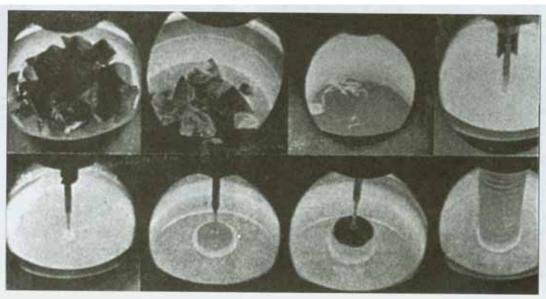

Time lapse sequence of boule being pulled from the melt in a Czochralski growth

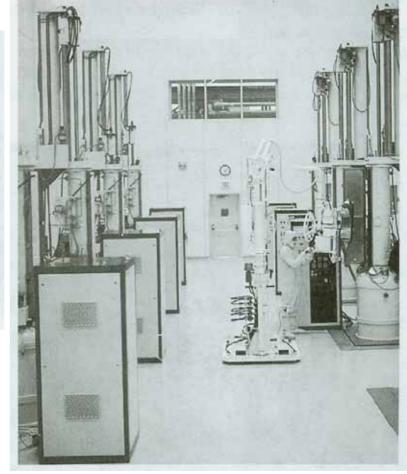

A 200-mm silicon growth facility

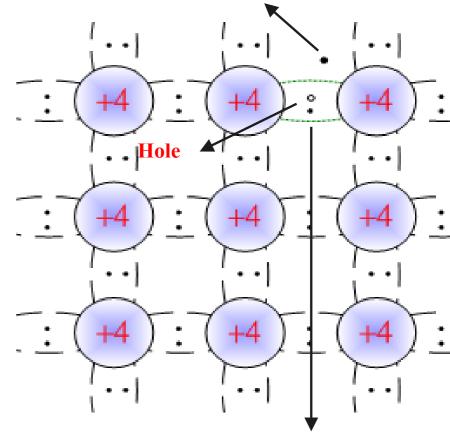

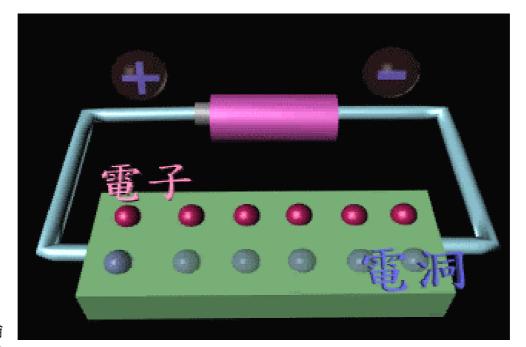

#### Electron and Hole

- Covalent band is broken at room temperature

- Produce the free electron

- Empty position hole

- Both electron and hole are called "carriers"

#### **Conduction electron**

- Electrons negative charge

- Holes positive charge

- The movement of carriers cause current in semiconductor

## **Ways of Doping**

Bad conductivity

#### Doping

- Substitutional impurity

- Interstitial impurity

- Interstitial-Substitutional impurity

中山電機系 黃義佑

## **Doping Type**

- Extrinsic semiconductor

- Doped the impurities into intrinsic semiconductor

- Acceptor

- p-type

- Donor

- n-type

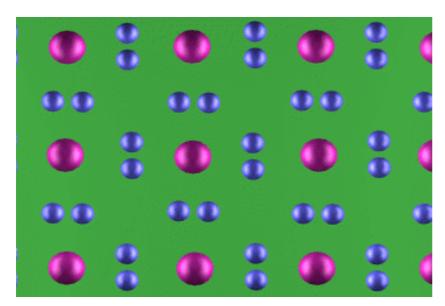

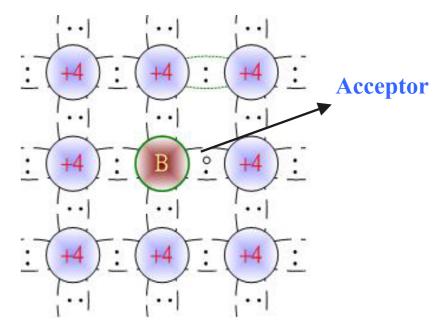

## p-type Semiconductor

#### Acceptor

- Adding the element of Group III (B, AI)

- Accept electron

- Majority carrier holes

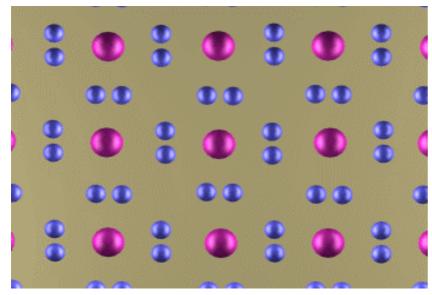

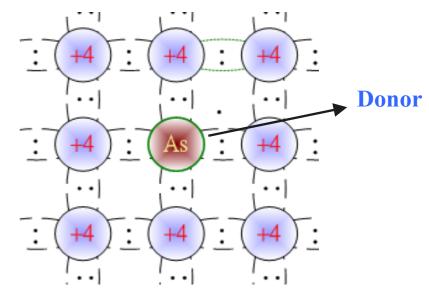

### n-type Semiconductor

#### Donor

- Adding the element of Group V (P, As)

- Supply electron

- Majority carrier electrons

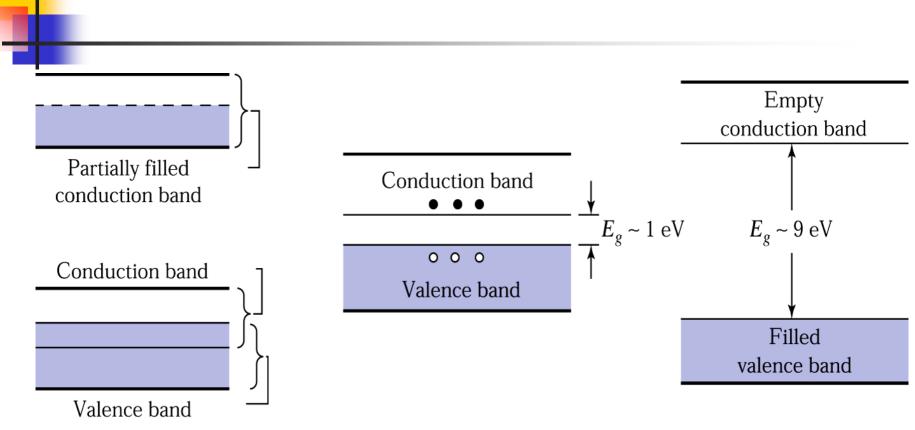

### **Energy Band Diagram**

Schematic energy band representations of (a) a conductor with two possibilities (either the partially filled conduction band shown at the upper portion or the overlapping bands shown at the lower portion), (b) a semiconductor, and (c) an insulator.

## **Energy-Band Diagram**

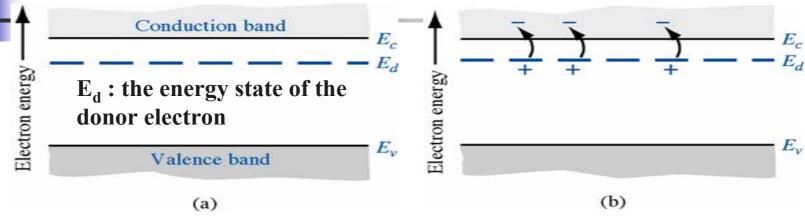

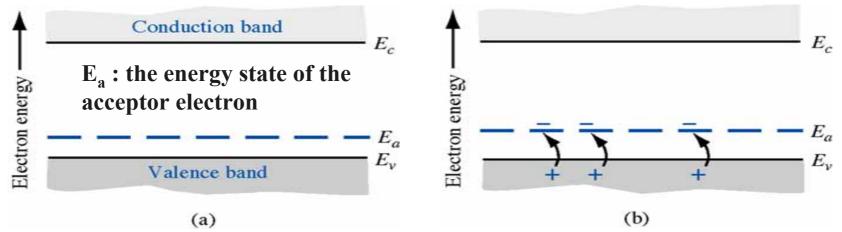

**Donor & Acceptor Energy State**

The energy-band diagram showing (a) the discrete donor energy state and (b) the effect of a donor state being ionized.

2005 SOC設計概論 中山電機系 黃義佑 Energy-band diagram showing (a) the discrete acceptor energy state and (b) the effect of a acceptor state being

## **Mobility and Resistivity**

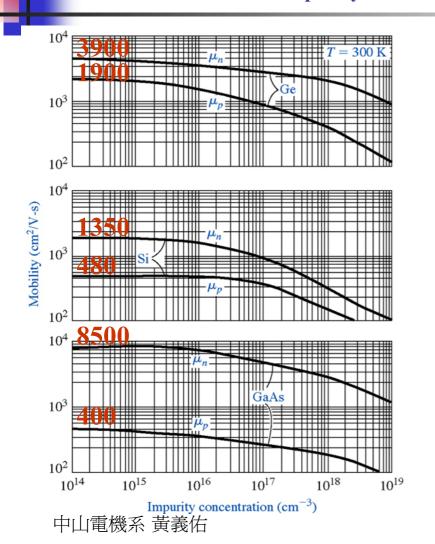

Mobilities and diffusivities in Si and GaAs at 300 K as a function of impurity concentration.

Resistivity versus impurity concentration for Si and GaAs.

#### **Measurement of Resistivity**

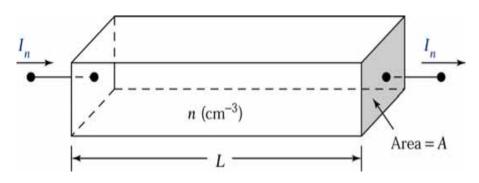

$$J_{drf} = q(\mu_n n + \mu_p p)E = \sigma E$$

$$\rho = \frac{1}{\sigma} = \frac{1}{q(n\mu_n + p\mu_p)} \qquad (\Omega - cm)$$

$$J = \frac{I}{A}; E = \frac{V}{L} \Rightarrow V = (\frac{L}{\sigma A})I = IR$$

Current conduction in a uniformly doped semiconductor bar with length *L* and cross-sectional area *A*.

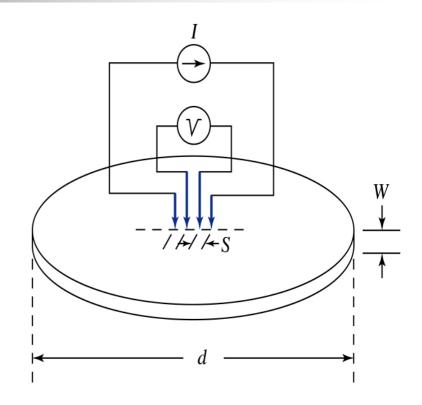

Measurement of resistivity using a four-point probe.

2005 SOC設計概論 中山電機系 黃義佑

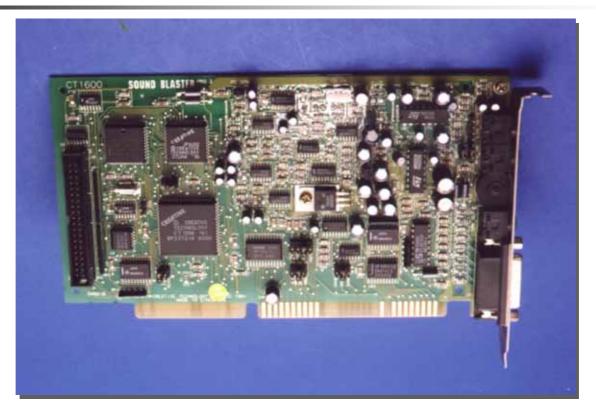

#### **Semiconductor Devices**

## - Components on Printed Circuit Board

Circuit types: Analog & Digital Circuits Component types: Passive & Active

## **Passive Component Structures**

- IC Resistor Structures: Parasitic Resistor Structures

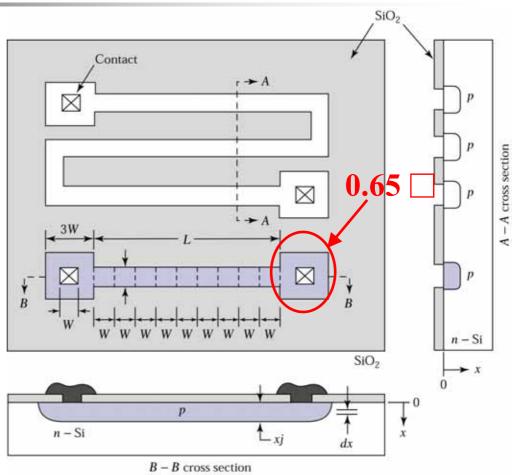

Integrated circuit resistors.

All narrow lines in the large square area have the same width W, and all contacts are the same size.

$$R \equiv \frac{1}{G} = \frac{L}{W} \left( \frac{1}{g} \right)$$

where 1/g: sheet resistance  $(\Omega/\Box)$

Example: L=90  $\mu$ m; W=10  $\mu$ m;

$$1/g=1 k\Omega/\square$$

R=(9+0.65\*2)\* 1 kΩ/

$$\square$$

=10.3 kΩ

2005 SOC設計概論

中山電機系 黃義佑

Examples of Resistor Structures in ICs

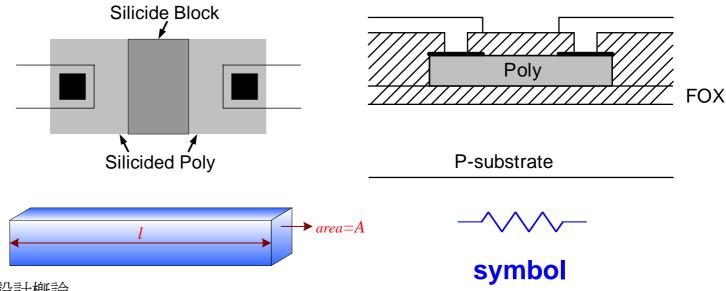

#### Resistor

- Polysilicon resistor

- is doped on an IC chip

- Linear

- Resistance is determined by length, area, and the resistivity of the material type

#### Interconnect Resistance

| Material      | ρ (Ω-m)              |  |  |

|---------------|----------------------|--|--|

| Silver (Ag)   | $1.6 \times 10^{-8}$ |  |  |

| Copper (Cu)   | $1.7 \times 10^{-8}$ |  |  |

| Gold (Au)     | $2.2 \times 10^{-8}$ |  |  |

| Aluminum (Al) | $2.7 \times 10^{-8}$ |  |  |

| Tungsten (W)  | $5.5 \times 10^{-8}$ |  |  |

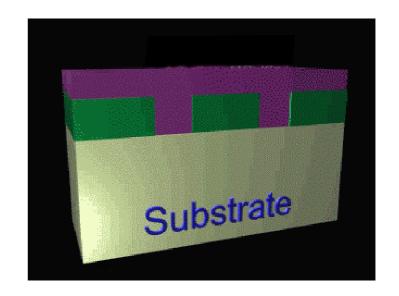

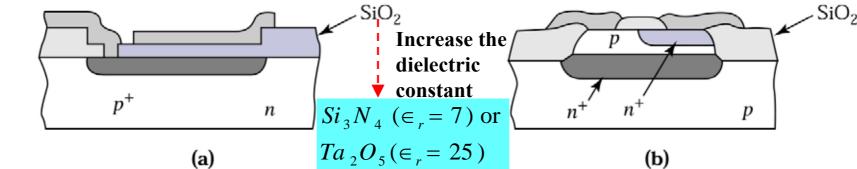

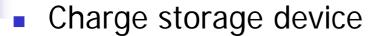

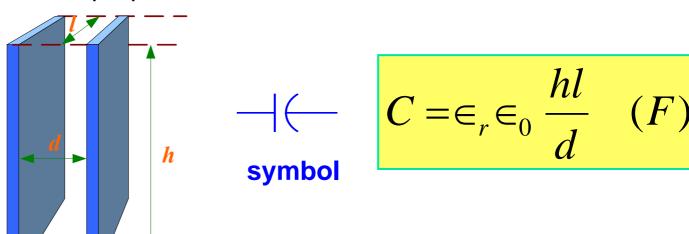

## Passive Component Structures Examples of Capacitors Structures in ICs

(a) Integrated MOS capacitor. (b) Integrated p-n junction capacitor.

$$C = \frac{\epsilon_{ox}}{d}$$

$(F/cm^2)$  ;  $\epsilon_{ox} = \epsilon_r \epsilon_0 = 3.9 \epsilon_0$

where  $\in_{ox}$ : dielectric permittivity of SiO<sub>2</sub>

$\in_r$ : dielectricconstant of SiO<sub>2</sub> = 3.9

$\in_0$ : permittivity of freespace (8.85×10<sup>-14</sup> F/cm)

- Memory Devices, esp. DRAM

- Two boards of semiconductor material as a capacitor

- Capacitances

- are proportional to the area (A=h\*I)

- are inverse proportional to the distance

2005 SOC設計概論 中山電機系 黃義佑

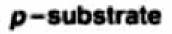

- 4

- Poly–poly (double poly process)

- Middle value

- Better noise immunity

- MMC (metal/metal capacitor)

2005 SOC設計概論 中山電機系 黃義佑

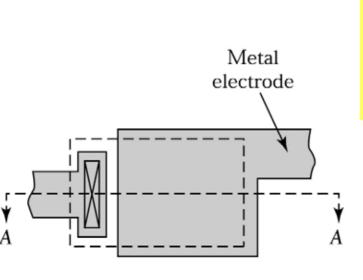

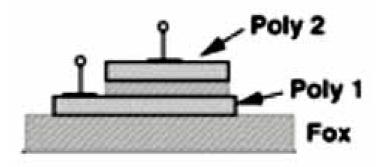

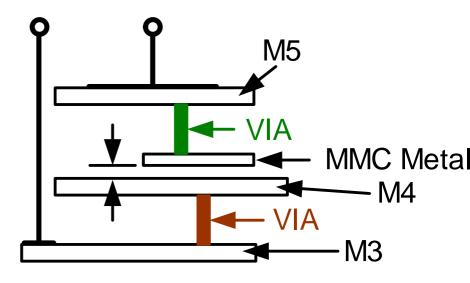

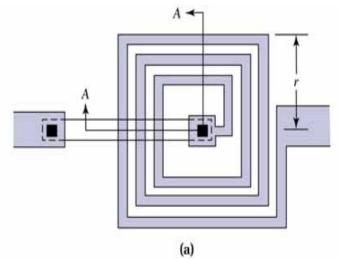

## Passive Component Structures Examples of Inductors Structures in ICs

Quality factor:  $Q = L\omega/R$

The higher the Q values; the lower the loss from resistance, hence the better the performance of the circuits.

There are some approaches to improve the Q values:

- (1) Reduce  $C_p$ : use low  $E_{ox}$  material

- (2) Reduce  $R_1$ : use thick film metal (e.g. Cu, Au)

- (3) Reduce  $R_{\text{sub-loss}}$ : use insulating substrate (SOI, quartz)

An estimated inductance of the square planar spiral inductor:

$$L \approx \mu_0 n^2 r \approx 1.2 \times 10^{-6} n^2 r$$

where  $\mu_0$ : permeability in vacuum

$$= (4\pi \times 10^{-7} H/m)$$

n: the number of turns

- (a) Schematic view of a spiral inductor on a silicon substrate.

- (b) Perspective view along A-A'

- The pn Junction Diode

- The Bipolar Junction Transistor (BJT)

- The Metal-Oxide-Semiconductor FET (MOSFETs)

- Complementary MOSFET (CMOS)

#### **PN Junction**

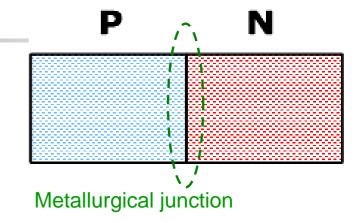

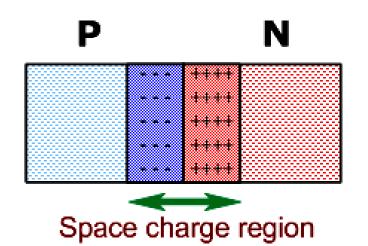

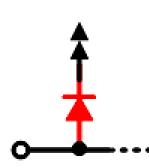

#### Diode

- p region

- Doped with acceptor impurities

- The positive charges atoms left

- n region

- Doped with donor impurities

- The negative charges atoms left

- Space charge region in thermal equilibrium

- Also called depletion region

- No mobile carrier exists

- Two forces exactly balance each other

- No current

2005 SOC設計概論 中山電機系 黃義佑

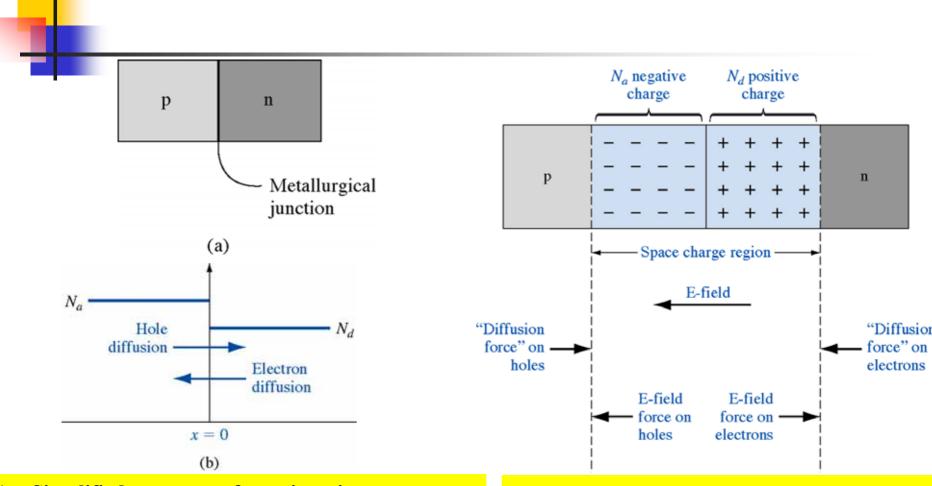

#### **PN Junction**

- (a) Simplified geometry of a pn junction;

- (b) Doping profile of an ideal uniformly doped pn junction

The space charge region, the electric field, and the forces acting on the charged carriers.

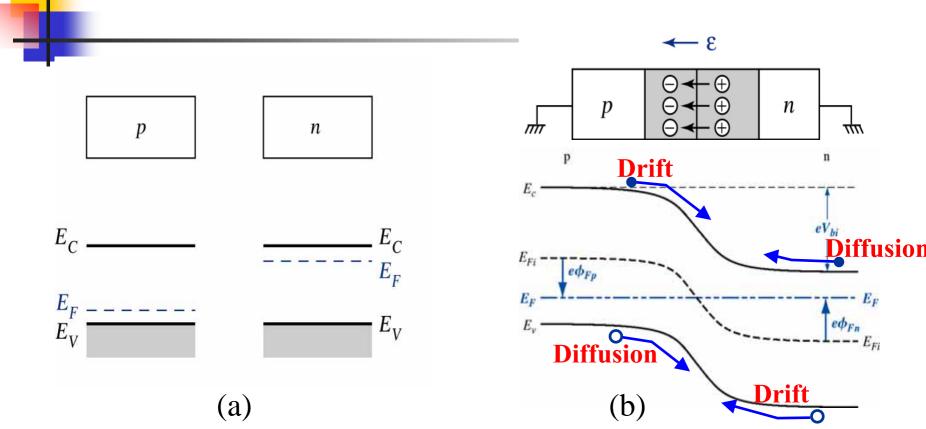

#### **Energy Band Diagram of the PN Junction**

(a) Uniformly doped p-type and n-type semiconductors before the junction is formed. (b) The energy band diagram of a p-n junction in thermal equilibrium.

2005 SOC設計概論 **Build-in voltage**:  $V_{bi} = \frac{kT}{q} \ln \left( \frac{N_a N_d}{n_i^2} \right) = V_t \ln \left( \frac{N_a N_d}{n_i^2} \right)$  35

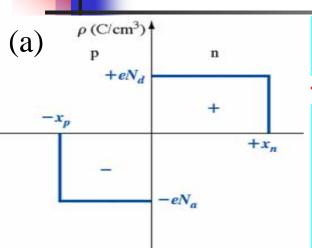

## Space Charge Density & Electric Field/Potential

uniformly doped pn junction

Poisson's Eq.:

$$\frac{d\phi(x)}{dx^2} = \frac{-\rho(x)}{\epsilon_s} = -\frac{dE(x)}{dx} \quad \text{(b)} \quad \text{p} \quad \text{for } x = 0$$

$$E = \int \frac{\rho(x)}{\epsilon_s} dx$$

$$= \frac{-qN_a}{\epsilon_s} (x + x_p); (-x_p \le x \le 0)$$

$$= \frac{-qN_d}{\epsilon_s} (x_n - x); (0 \le x \le x_n)$$

$$\phi(x) = -\int E(x) dx$$

- (a) The space charge density in a uniformly doped pn junction assuming the abrupt junction approximation

- (b) Electric field in the space charge region in a uniformly doped pn junction

- (c) Electric potential through the space charge region in a uniformly doped pn junction

## **Space Charge Density & Electric Field/Potential**

**One-sided abrupt junction**

- (a) One-sided abrupt junction (with  $N_A$  >>  $N_D$ ) in thermal equilibrium.

- (b) Space charge distribution.

- (c) Electric-field distribution.

- (d) Potential distribution with distance, where  $V_{bi}$  is the built-in potential.

$$W = \left\{ \frac{2 \in_{s} V_{bi}}{q} \left[ \frac{N_a + N_d}{N_a N_d} \right] \right\}^{1/2}$$

$$\cong X_n = \sqrt{\frac{2 \in_{s} V_{bi}}{q N_d}}$$

(a) (b) (c) (d)

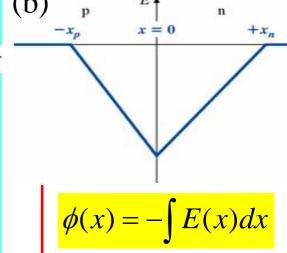

## The Uniformly Doped pn Junction Diode

$$W = \left\{ \frac{2 \in_{s} V_{bi}}{q} \left[ \frac{N_{a} + N_{d}}{N_{a} N_{d}} \right] \right\}^{1/2} W = \left\{ \frac{2 \in_{s} (V_{bi} + V_{R})}{q} \left[ \frac{N_{a} + N_{d}}{N_{a} N_{d}} \right] \right\}^{1/2} W = \left\{ \frac{2 \in_{s} (V_{bi} - V_{a})}{q} \left[ \frac{N_{a} + N_{d}}{N_{a} N_{d}} \right] \right\}^{1/2} W = \left\{ \frac{2 \in_{s} (V_{bi} - V_{a})}{q} \left[ \frac{N_{a} + N_{d}}{N_{a} N_{d}} \right] \right\}^{1/2} W = \left\{ \frac{2 \in_{s} (V_{bi} - V_{a})}{q} \left[ \frac{N_{a} + N_{d}}{N_{a} N_{d}} \right] \right\}^{1/2} W = \left\{ \frac{2 \in_{s} (V_{bi} - V_{a})}{q} \left[ \frac{N_{a} + N_{d}}{N_{a} N_{d}} \right] \right\}^{1/2} W = \left\{ \frac{2 \in_{s} (V_{bi} - V_{a})}{q} \left[ \frac{N_{a} + N_{d}}{N_{a} N_{d}} \right] \right\}^{1/2} W = \left\{ \frac{2 \in_{s} (V_{bi} - V_{a})}{q} \left[ \frac{N_{a} + N_{d}}{N_{a} N_{d}} \right] \right\}^{1/2} W = \left\{ \frac{2 \in_{s} (V_{bi} - V_{a})}{q} \left[ \frac{N_{a} + N_{d}}{N_{a} N_{d}} \right] \right\}^{1/2} W = \left\{ \frac{2 \in_{s} (V_{bi} - V_{a})}{q} \left[ \frac{N_{a} + N_{d}}{N_{a} N_{d}} \right] \right\}^{1/2} W = \left\{ \frac{2 \in_{s} (V_{bi} - V_{a})}{q} \left[ \frac{N_{a} + N_{d}}{N_{a} N_{d}} \right] \right\}^{1/2} W = \left\{ \frac{2 \in_{s} (V_{bi} - V_{a})}{q} \left[ \frac{N_{a} + N_{d}}{N_{a} N_{d}} \right] \right\}^{1/2} W = \left\{ \frac{2 \in_{s} (V_{bi} - V_{a})}{q} \left[ \frac{N_{a} + N_{d}}{N_{a} N_{d}} \right] \right\}^{1/2} W = \left\{ \frac{2 \in_{s} (V_{bi} - V_{a})}{q} \left[ \frac{N_{a} + N_{d}}{N_{a} N_{d}} \right] \right\}^{1/2} W = \left\{ \frac{2 \in_{s} (V_{bi} - V_{a})}{q} \left[ \frac{N_{a} + N_{d}}{N_{a} N_{d}} \right] \right\}^{1/2} W = \left\{ \frac{2 \in_{s} (V_{bi} - V_{a})}{q} \left[ \frac{N_{a} + N_{d}}{N_{a} N_{d}} \right] \right\}^{1/2} W = \left\{ \frac{2 \in_{s} (V_{bi} - V_{a})}{q} \left[ \frac{N_{a} + N_{d}}{N_{a} N_{d}} \right] \right\}^{1/2} W = \left\{ \frac{2 \in_{s} (V_{bi} - V_{a})}{q} \left[ \frac{N_{a} + N_{d}}{N_{a} N_{d}} \right] \right\}^{1/2} W = \left\{ \frac{2 \in_{s} (V_{bi} - V_{a})}{q} \left[ \frac{N_{a} + N_{d}}{N_{a} N_{d}} \right] \right\}^{1/2} W = \left\{ \frac{2 \in_{s} (V_{bi} - V_{a})}{q} \left[ \frac{N_{a} + N_{d}}{N_{a} N_{d}} \right] \right\}^{1/2} W = \left\{ \frac{2 \in_{s} (V_{bi} - V_{a})}{q} \left[ \frac{N_{a} + N_{d}}{N_{a} N_{d}} \right] \right\}^{1/2} W = \left\{ \frac{2 \in_{s} (V_{bi} - V_{a})}{q} \left[ \frac{N_{a} + N_{d}}{N_{a} N_{d}} \right] \right\}^{1/2} W = \left\{ \frac{2 \in_{s} (V_{bi} - V_{a})}{q} \left[ \frac{N_{a} + N_{d}}{N_{a} N_{d}} \right] \right\}^{1/2} W = \left\{ \frac{2 \in_{s} (V_{bi} - V_{a})}{q} \left[ \frac{N_{a} + N_{d}}{N_{a} N_{d}} \right] \right\}^{1/2} W = \left\{ \frac{2 \in_{s} (V_{bi} - V_{a})}{q} \left[ \frac{N_{a} + N_{d}}{N_{a$$

Schematic representation of depletion layer width and energy band diagrams of a *p-n* junction under various biasing conditions. (a) Thermal-equilbrium condition. (b) Reverse-bias condition. (c) Forward-bias condition.

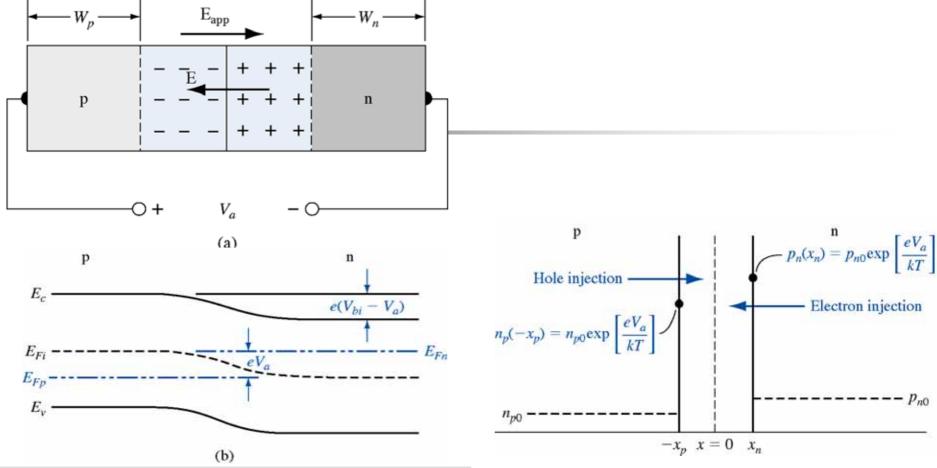

## Ideal Current-Voltage Relationship of Diode

- (a) A pn junction with an applied forwardbias voltage showing the directions of the electric field induced by  $V_a$  and the space charge electric field.

- (b) Energy-band diagram of the forwardbiased pn junction

Excess minority carrier concentrations at the space charge edges generated by the forward-bias voltage

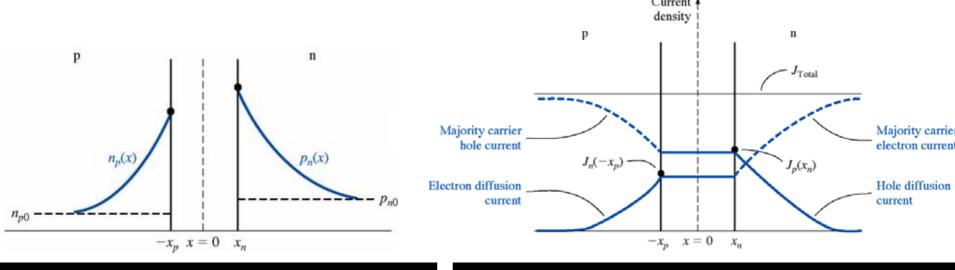

#### **Ideal PN Junction Current**

## Steady-state minority carrier concentrations in a pn junction under forward bias

$$J_{p}(x_{n}) = \frac{qD_{p}p_{n0}}{L_{p}} [\exp(\frac{qV_{a}}{kT}) - 1]$$

$$J_{n}(-x_{p}) = \frac{qD_{n}n_{p0}}{L_{n}} [\exp(\frac{qV_{a}}{kT}) - 1]$$

$$J_{D} = J_{p}(x_{n}) + J_{n}(-x_{p})$$

$$= [\frac{qD_{p}p_{n0}}{L_{p}} + \frac{qD_{n}n_{p0}}{L_{n}}] [\exp(\frac{qV_{a}}{kT}) - 1]$$

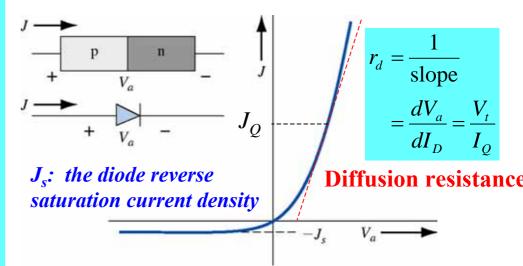

$$= J_{s} [\exp(\frac{qV_{a}}{kT}) - 1] \approx J_{s} \exp(\frac{qV_{a}}{kT})$$

Ideal electron and hole current components through a pn junction under forward bias.

Ideal I-V characteristic of a pn junction diode

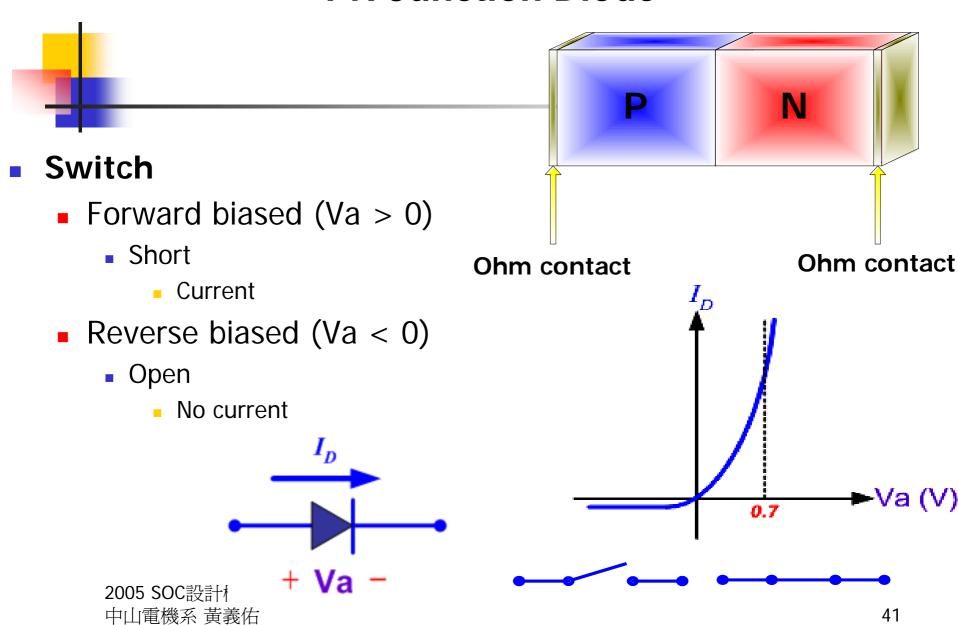

#### **PN Junction Diode**

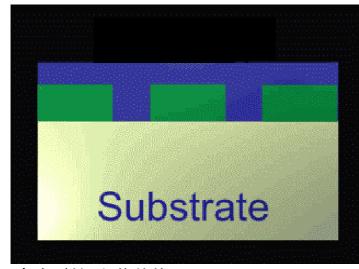

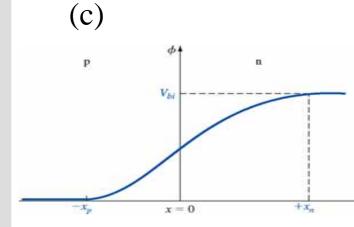

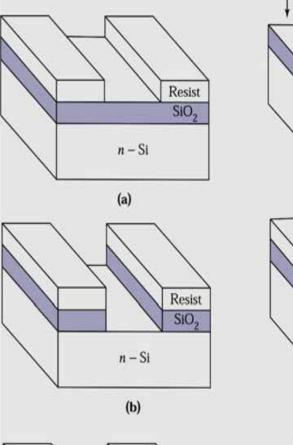

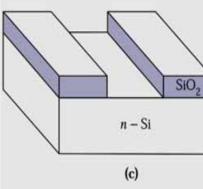

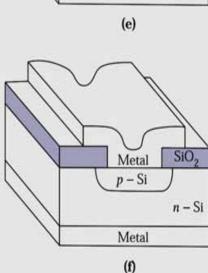

# Fabrication Processes of PN Junction Diode

- (a) The wafer after the development.

- (b) The wafer after SiO<sub>2</sub> removal.

- (c) The final result after a complete lithography process.

- (d) A *p-n* junction is formed in the diffusion or implantation process.

- (e) The wafer after metallization.

- (f) A *p-n* junction after the compete process.

2005 SOC設計概論 中山電機系 黃義佑

Dopant gas

accelerated impurity ions

p - Si

(d)

p - Si

n - Si

SiO.

n - Si

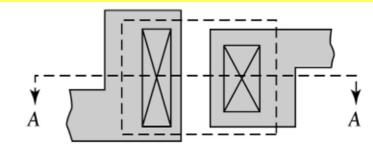

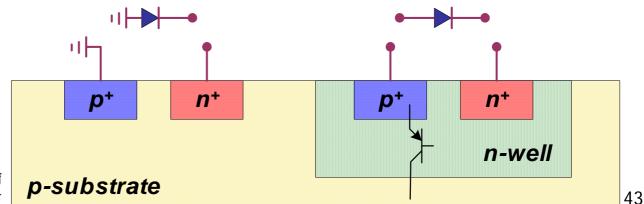

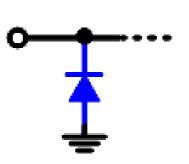

## **Application of Diode**

- Used for protection circuit

- In substrate

- Remain reverse biased

- In n-well

- Prevent forward pn junction

- Substantial current flow

2005 SOC設計概論 中山電機系 黃義佑