# Chapter 3: ULSI Manufacturing Technology – (d) Etch

#### Reference

- 1. Semiconductor Manufacturing Technology : Michael Quirk and Julian Serda (2001)

- 2. 國家矽導計畫-教育部晶片法商學程教材 (2004)

- 3. Semiconductor Physics and Devices- Basic Principles(3/e) : Donald A. Neamen (2003)

- 4. Semiconductor Devices Physics and Technology (2/e) : S. M. Sze (2002)

- 5. ULSI Technology: C. Y. Chang, S. M. Sze (1996)

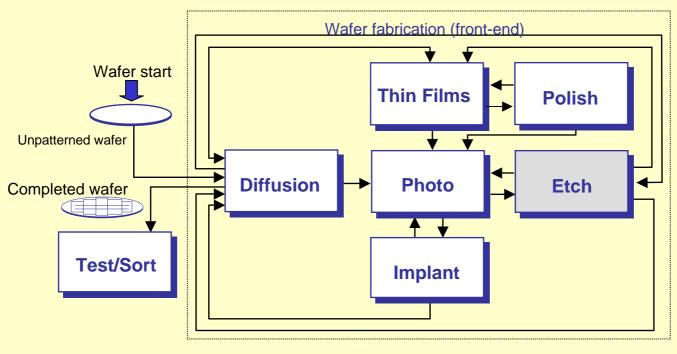

## Applications for Wafer Etch in CMOS Technology

#### **Process Flow in a Wafer Fab:**

#### **Etch Process & Etch Parameters**

#### **Categories of Etch Processes:**

- Wet Etch

- Dry Etch

- Three Major Materials to be Etched:

- -Silicon

- -Dielectric

- -Metal

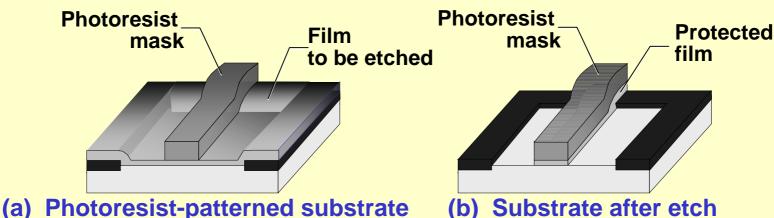

- Patterned Etch Versus Unpatterned Etch

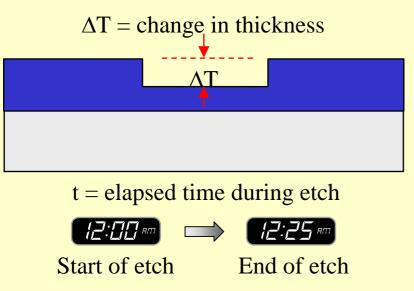

**Etch rate**

**Etch profile**

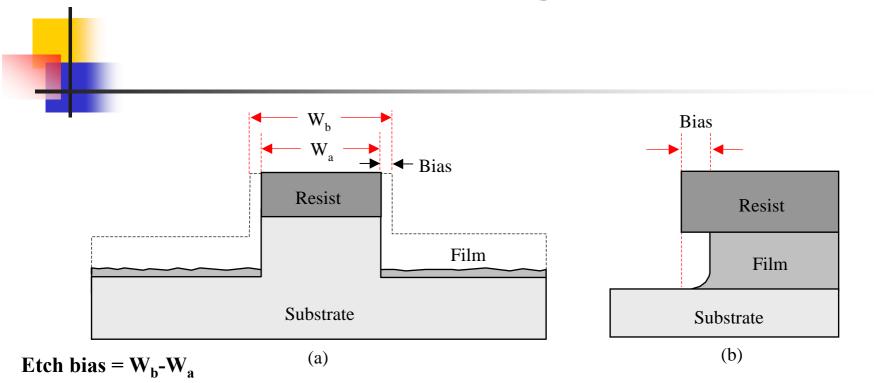

**Etch bias**

Selectivity

**Uniformity**

**&**Residues

Polymer formation

**♦**Plasma-induced damage

**▶**Particle contamination and defects

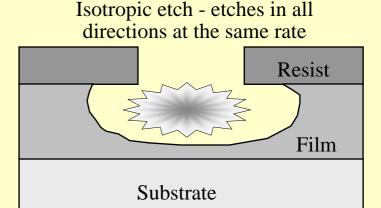

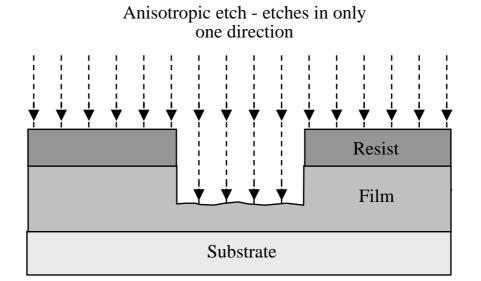

#### **Isotropic & Anisotropic Etch**

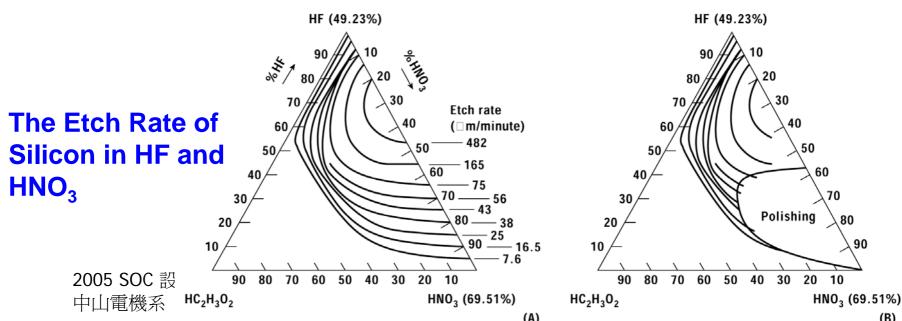

#### **Etch Rate & Wet Chemical Isotropic Etch**

**Anisotropic Etch with Vertical Etch Profile**

2005 SOC 設計概論 中山電機系 黃義佑

## Advantages of Dry Etch over Wet Etch

- 1. Etch profile is anisotropic with excellent control of sidewall profiles.

- 2. Good CD control.

- 3. Minimal resist lifting or adhesion problems.

- 4. Good etch uniformity within wafer, wafer-to-wafer and lot-to-lot.

- 5. Lower chemical costs for usage and disposal.

## Sidewall Profiles for Wet Etch Versus Dry Etch

| Type of Etch | Sidewall Profile                                  | Diagram |

|--------------|---------------------------------------------------|---------|

| Wet Etch     | Isotropic                                         |         |

|              | Isotropic (depending on equipment & parameters)   |         |

| Dry Etch     | Anisotropic (depending on equipment & parameters) |         |

|              | Anisotropic –<br>Taper                            |         |

|              | Silicon Trench                                    |         |

2005 SOC

中山電機系 黃義佑

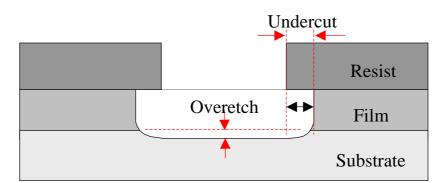

#### **Etch Bias & Etching Undercut**

$\mathbf{W}_{b}$  = the original linewidth on photoresist before etch.

$\mathbf{W}_{\mathbf{a}}$  = the final linewidth of the etched material after resist removal.

2005 SOC 設計概論 中山電機系 黃義佑

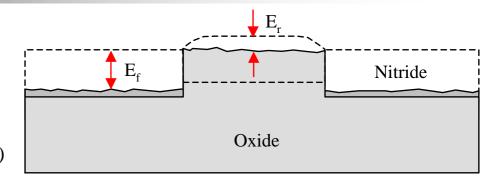

### **Etch Selectivity & Etch Uniformity**

Etch selectivity:

$$S_R = \frac{E_f}{E_r}$$

$E_f$  = the etch rate of the film undergoing etch

$E_r$  = the etch rate of the masking layer (e.g. photoresist)

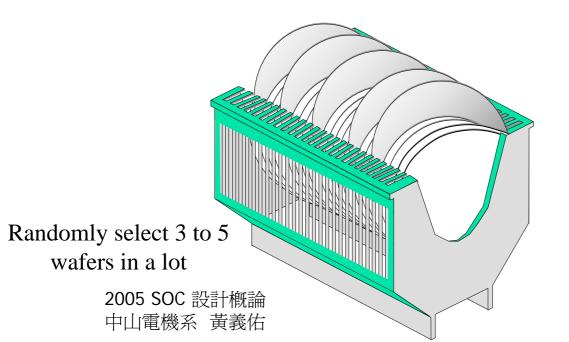

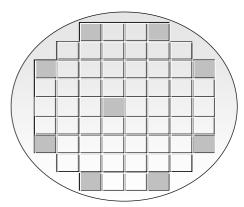

Measure etch rate at 5 to 9 locations on each wafer, then calculate etch uniformity for each wafer and compare wafer-to-wafer.

9

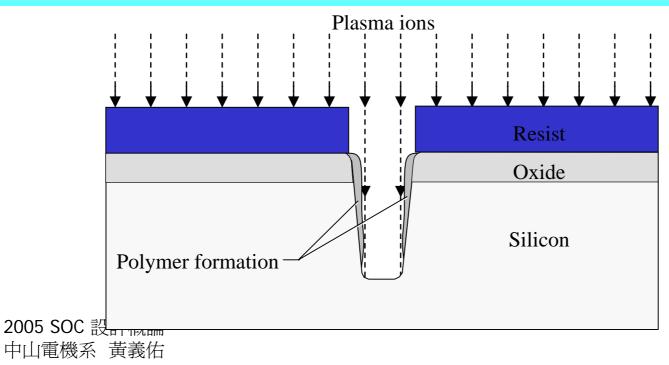

## Polymer Sidewall Passivation for Increased Anisotropy

The result is better control of CD of patterened structures. The polymers come from PR carbon converted into polymers during etching and combines with etching gases (i.e.  $C_2F_4$ ) and etch by-products to form this sidewall polymer.

The polymer chains have strong C-F bonds that are difficult to oxidize and remove. However, the polymers must be removed after the etch process or device yield and reliability is affected. The cleaning of the sidewall often requires special gas chemistry for a plasma stripping process or possible a wet clean using strong solvents followed by DI water rinsing.

10

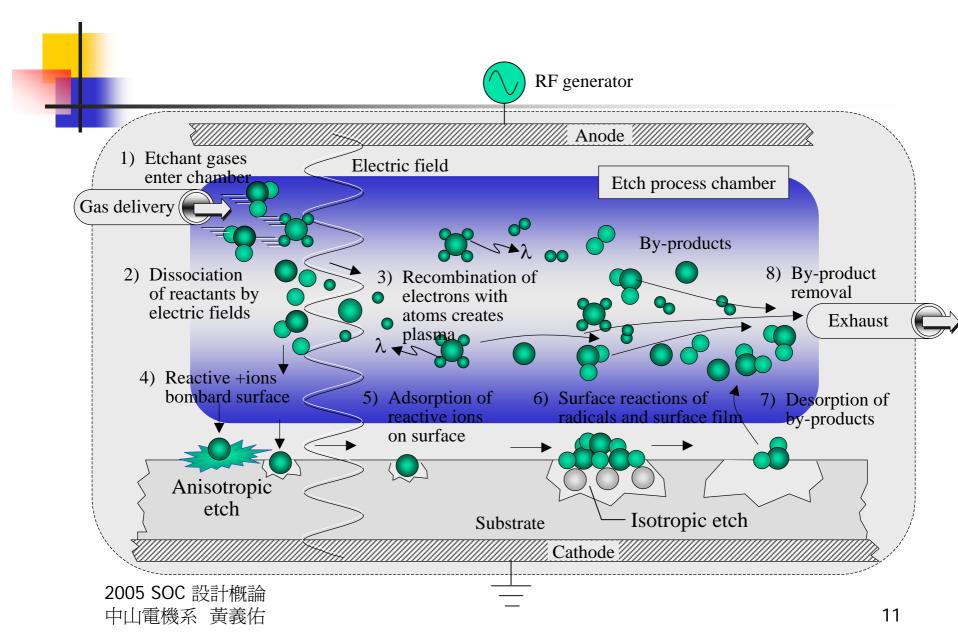

#### Plasma Etch Process of a Silicon Wafer

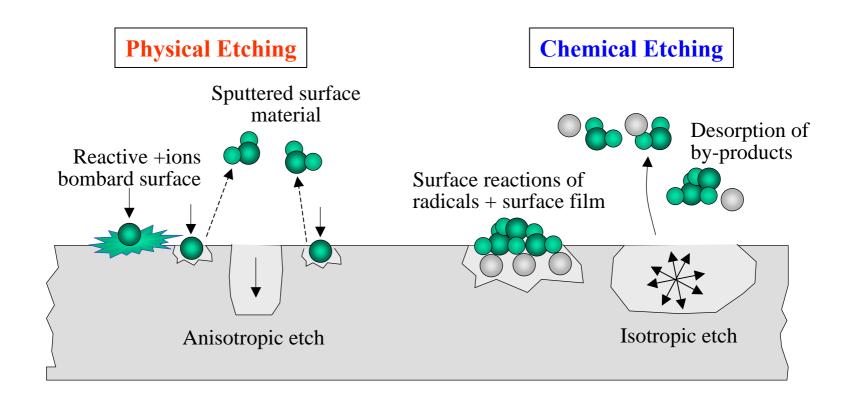

### **Chemical and Physical Dry Etch Mechanisms**

## **Chemical Versus Physical Dry Plasma Etching**

|   | Etch Parameter   | Physical Etch<br>(RF field<br>perpendicular<br>to wafer<br>surface) | Physical Etch<br>(RF field<br>parallel to<br>wafer surface) | Chemical Etch                                  | Combined<br>Physical and<br>Chemical                                                                 |

|---|------------------|---------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------|

|   | Etch Mechanism   | Physical ion sputtering                                             | Radicals in plasma reacting with wafer surface*             | Radicals in liquid reacting with wafer surface | In dry etch,<br>etching includes<br>ion sputtering<br>and radicals<br>reacting with<br>wafer surface |

|   | Sidewall Profile | Anisotropic                                                         | Isotropic                                                   | Isotropic                                      | Isotropic to<br>Anisotropic                                                                          |

|   | Selectivity      | Poor/difficult to increase (1:1)                                    | Fair/good (5:1 to 100:1)                                    | Good/excellent (up to 500:1)                   | Fair/good (5:1 to 100:1)                                                                             |

|   | Etch Rate        | High                                                                | Moderate                                                    | Low                                            | Moderate                                                                                             |

| ( | CD Control       | Fair/good                                                           | Poor                                                        | Poor to non-<br>existent                       | Good/excellent                                                                                       |

<sup>\*</sup> Used primarily for stripping and etchback operations.

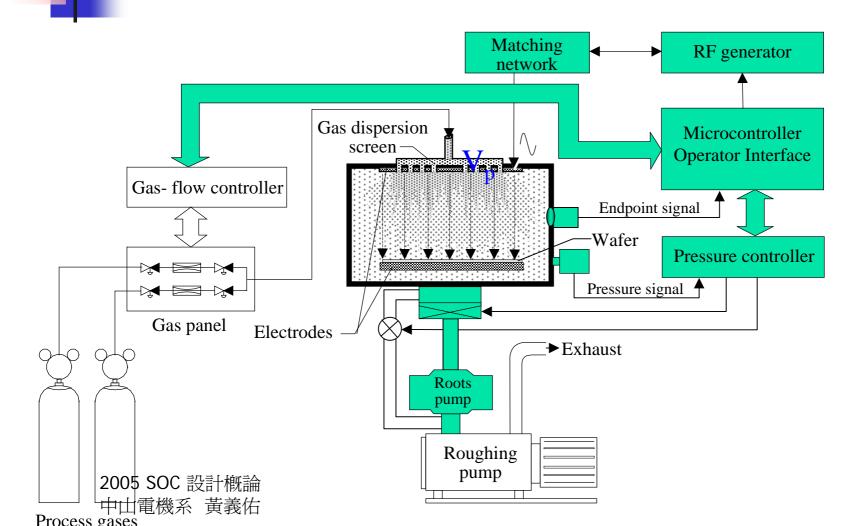

### **Parallel Plate Plasma Etching**

Physical and chemical etch mechanisms occur in both the plasma etch mode and the RIE mode

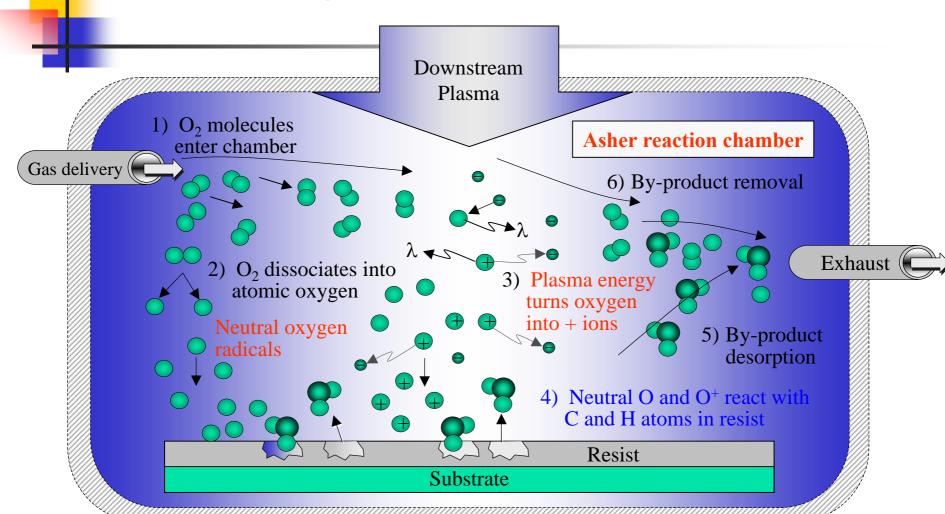

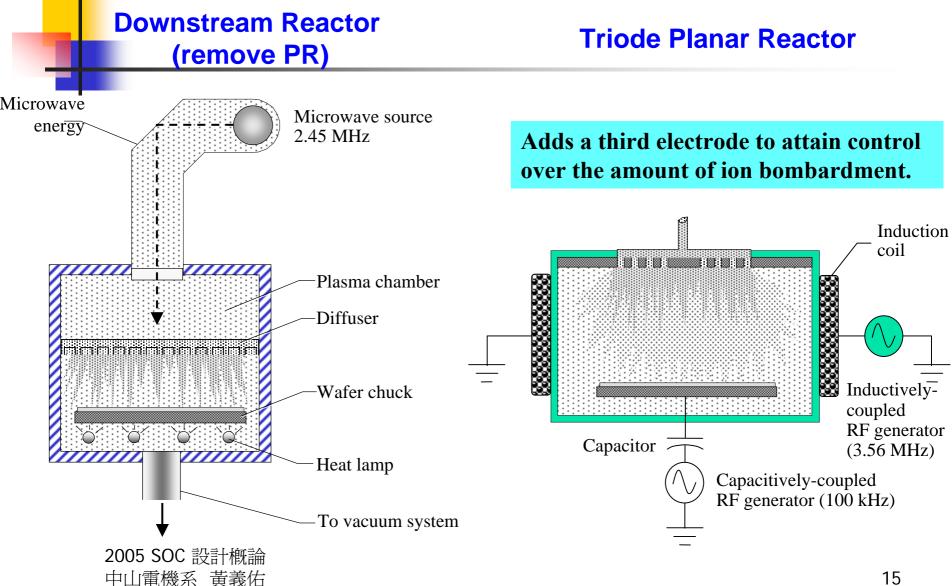

### Downstream etch systems & Triode planar reactor

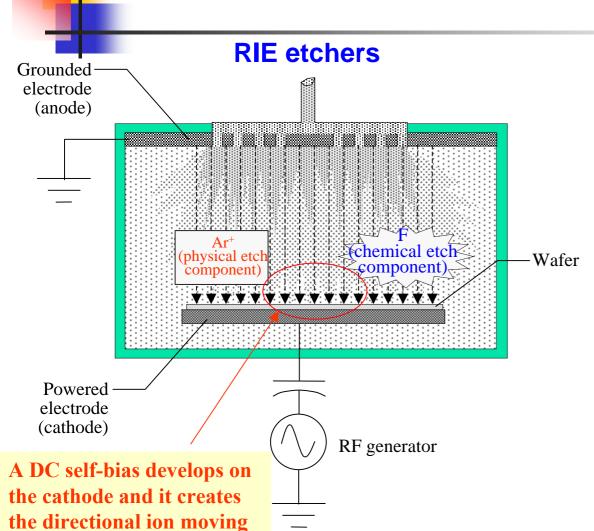

## Reactive ion etch (RIE) & High-density plasma (HDP) etchers

toward wafer.

#### **HDP Etcher**

Figure 11.21 Applied Materials high-density plasma silicon etch system (photo courtesy Applied Materials).

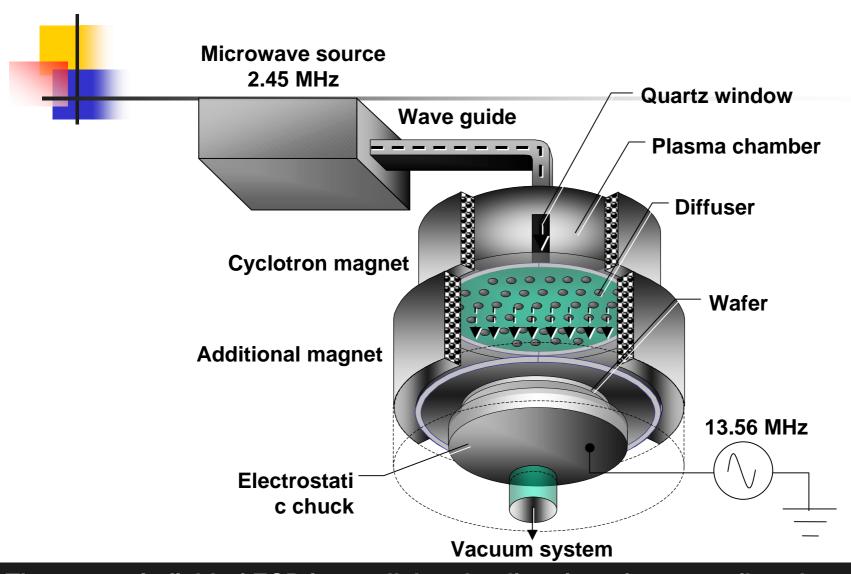

#### **Electron Cyclotron Reactor (ECR)**

The magnetic field of ECR is parallel to the direction of reactant flow that causes free electrons to move in a spiral path due to the magnetic force → dense plasma

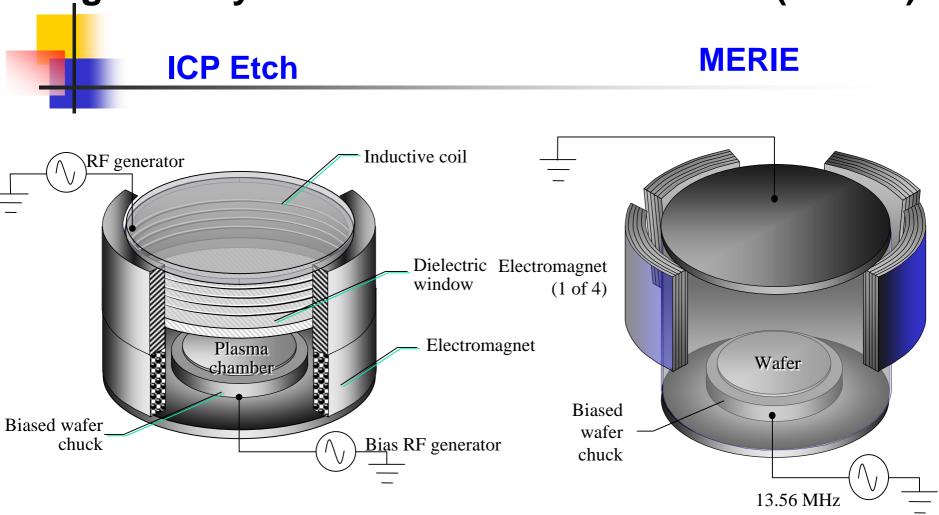

## Inductively Coupled Plasma (ICP) & Magnetically Enhanced Reactive Ion Etch (MERIE)

The wafer can be biased to have both chemical and physical etching. This reactor can achieve anisotropic sidewall profiles in high-aspect ratio opening.

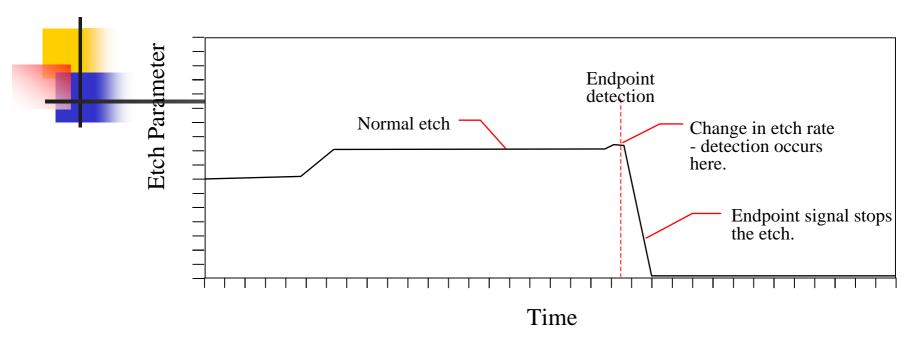

## **Endpoint Detection for Plasma Etching**

## **Endpoint Detection**

2005 SOC 設計概論 中山電機系 黃義佑

Photograph courtesy of Advanced Micro Devices, Lam Rainbow etcher

## **Dry Etch**

#### **Dry Etch Applications**

- **<b>凌Dielectric Dry Etch**

- -Oxide

- -Silicon Nitride

- **♦**Silicon Dry Etch

- -Polysilicon

- -Single-Crystal Silicon

- **Metal Dry Etch**

- Aluminum and Metal Stacks

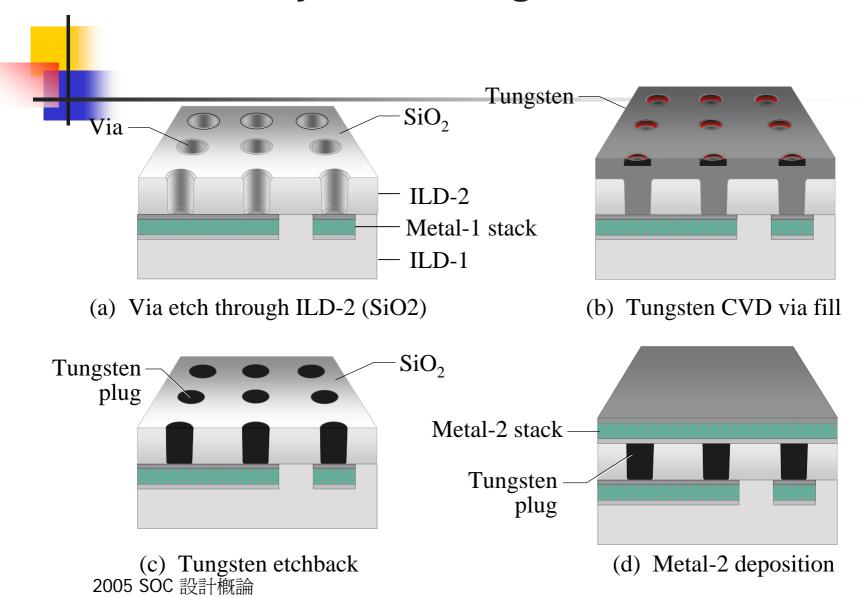

- -Tungsten Etchback

- –Contact Metal Etch

2005 SOC 設計概論 中山電機系 黃義佑

#### **Requirements for Successful Dry Etch**

- 1. High selectivity to avoid etching materials that are not to be etched (primarily photoresist and underlying materials).

- 2. Fast etch rate to achieve an acceptable throughput of wafers.

- 3. Good sidewall profile control.

- 4. Good etch uniformity across the wafer.

- 5. Low device damage.

- 6. Wide process latitude for manufacturing.

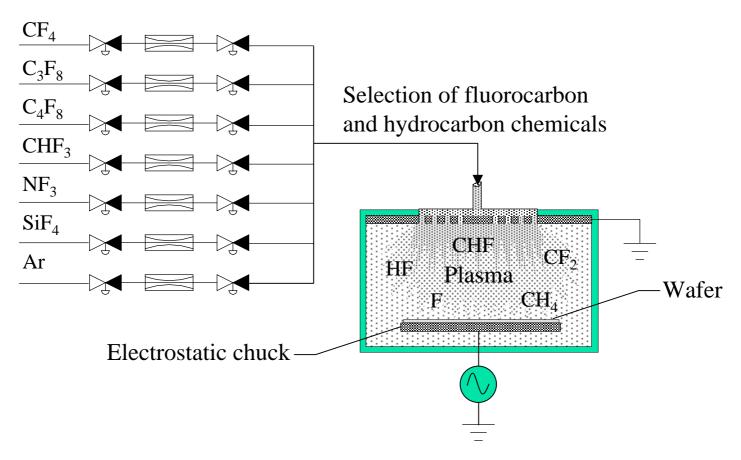

#### **Dielectric Dry Etch - Oxide Etch**

- ► For 0.18um DRAM: oxide etching aspect ratios = 6:1; selectivity = 50:1

- ► The oxide plasma etching process is commonly based on fluorocarbon chemistry

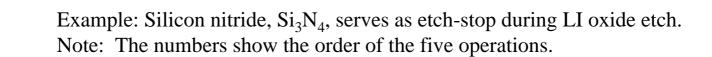

## **Underlying Material Selectivity**

Doped oxide CVD Nitride CVD Oxide CMP Oxide etch Nitride etch LI Oxide p-well n-well p- Epitaxial Layer p+ Silicon Substrate

**Etch Stop Hard Mask Layer**

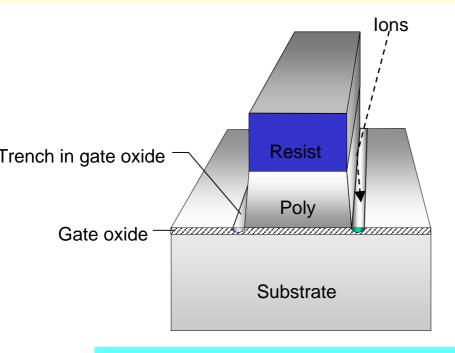

#### Polysilicon Gate Etch & Si Trench Etch

#### **Polysilicon Gate Etch Process Steps:**

- 1. Breakthrough step to remove native oxide and surface contaminants

- 2. Main-etch step to remove most polysilicon without damage to gate oxide

- 3. Overetch step to remove remaining residues and poly stringers while maintaining high selectivity to gate oxide

**Undesirable Microtrenching during Polysilicon Gate Etching**

**Silicon Trench Etching**

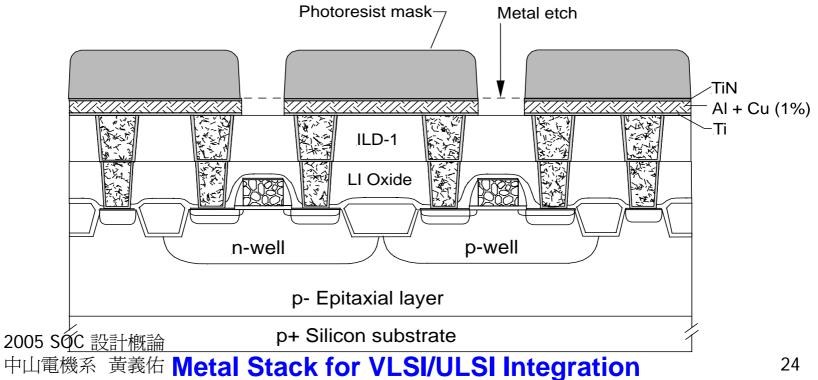

#### **Metal Dry Etch**

#### Typical Steps for Etching Metal Stacks

- Breakthrough step to remove native oxide.

- ARC layer etch (may be combined with above step).

- 3. Main etch step of aluminum.

- Overetch step to remove residue. It may be a continuation of main etch step. 4.

- **5**. Barrier layer etch.

- 6. Optional residue removal process to prevent corrosion.

- Resist removal.

### **Metal Dry Etch - Tungsten Etchback**

中山電機系 黃義佑

#### **Wet Etch**

| Parameter     | Explanation                                                        | Difficulty to Control                                                                       |  |

|---------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|

| Concentration | Solution concentration (e.g., ratio of NH4F:HF for etch an oxide). | Most difficult parameter to control because the bath concentration is continually changing. |  |

| Time          | Time of wafer immersion in the wet chemical bath.                  | Relatively easy to control.                                                                 |  |

| Temperature   | Temperature of wet chemical bath.                                  | Relatively easy to control.                                                                 |  |

| Agitation     | Agitation of the solution bath.                                    | Moderate difficulty to properly control.                                                    |  |

**Wet Etch Parameters**

#### Wet Etch Rate of Oxide and Silicon

**Approximate Oxide Etch Rates in BHF Solution at 25° C**

| <b>Table 16.8</b> <sup>1</sup> Approximate Oxide Etch Rates in BHF Solution at 25°C <sup>a</sup> |                              |                   |  |  |  |

|--------------------------------------------------------------------------------------------------|------------------------------|-------------------|--|--|--|

| Type of Oxide                                                                                    | Density (g/cm <sup>3</sup> ) | Etch Rate (nm/s)  |  |  |  |

| Dry grown                                                                                        | 2.24 - 2.27                  | 1                 |  |  |  |

| Wet grown                                                                                        | 2.18 - 2.21                  | 1.5               |  |  |  |

| CVD deposited                                                                                    | < 2.00                       | $1.5^{b} - 5^{c}$ |  |  |  |

| Sputtered                                                                                        | < 2.00                       | 10 – 20           |  |  |  |

- a) 10 parts of 454 g NH<sub>4</sub>F in 680 ml H<sub>2</sub>O and one part 48% HF

- b) Annealed at approximately 1000°C for 10 minutes

- c) Not annealed

### **Wet Anisotropic Etching**

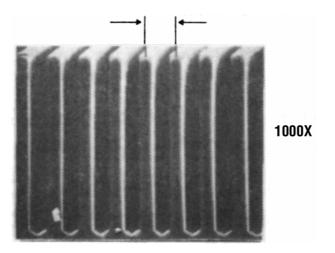

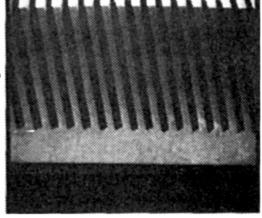

SEM TOP VIEW (100) DI ETCH

SEM CROSSECTIONAL VIEW (100) DI ETCH

Figure 11.6 (100) silicon wafers after directional etching in KOH, isopropyl alcohol, and water. The upper photo shows a 50-mm-deep etch. The lower 2005 photographs are of 80-mm-deep trenches etched at 10 mm pitch on (110) and 107 off (110) (after Bean, ©1978 IEEE).

$160~\mu m$  DEEP

## Photoresist Removal Atomic Oxygen Reaction with Resist in Asher